Solbourne Computer

Click here for more info about and larger photographs of the hardware.

Solbourne Computer was an engineering workstation company founded by Doug MacGregor in 1986. MacGregor had designed the microcode for the Motorola 68010 and 68020 microprocessors and then pursued a doctorate in Information Science at Kyoto University. After a presentation in Japan he met a senior executive from Matsushita Corporation who ultimately funded Solbourne (originally called SAE for "Solutions are Everything") in the unlikely location of Longmont, Colorado.

My first job out of college with was with the Technical Workstation Group at Hewlett-Packard in Fort Collins, Colorado. I hired into a group run by Ken Watts. I had no idea how lucky I was to have him for a manager. He was considered one of the best managers in the organization who fought tooth-and-nail for his engineers. At the time Ken's group was designing graphics systems for HP workstations but he knew Doug MacGregor because HP had been one of the first customers of the Motorola 68k line. Doug called on Ken as he started to build a team for his new company and Ken did the unthinkable in those days ...leave HP... along with several engineers. I ended up working for a manager I can barely remember now but disliked intensely at the time. About a year and a half later I got home from the movies with my soon-to-be-wife and found a message from Ken on the answering machine asking if I was done "playing around at HP" and wanted to come down to work with him again. It wasn't a hard decision and I left mother HP for the world of start-ups. Sadly Ken passed away a couple of years later.

Some of the best and some of the worst times I have had as an engineer were at Solbourne. The company was a fantastic place to work in the beginning. We did some amazing engineering and had a great time. The first symmetric multiprocessing SPARC server. Perhaps the first synchronous DRAM (a VRAM with built-in raster-ops). A fast track graphics project I managed that went from initial kickoff to fully functional PCB prototype in 2 weeks. But some major strategic decisions doomed the company to be nothing more than a footnote in the history of computing. The company lived on for many years providing consulting services and solutions based on Oracle Applications and technologies before being acquired by Deloitte.

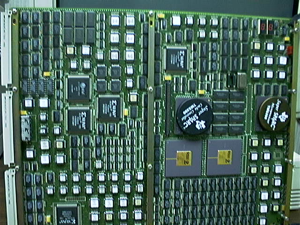

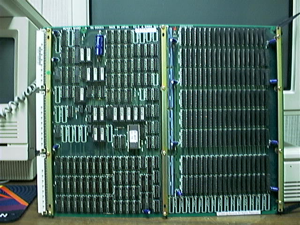

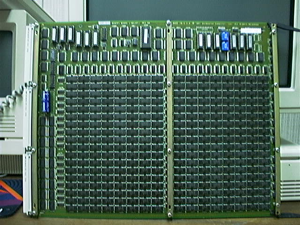

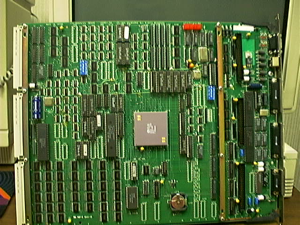

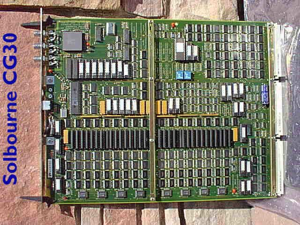

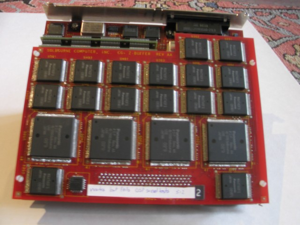

Someday I'd like to document the history of Solbourne. It was an incredible time for everyone involved. At one point I took the pictures on this page of some of the hardware. Sorry for the poor quality. I had only a terrible Apple QuickTake 200 camera that I had gotten as a free promotion from Apple.

Solbourne's first products were based on a cache-coherent multiprocessor bus called K-bus. It supported up to 11 slots using TTL signaling at 20 MHz and was used in three computers: an initial desk side server with 7 slots, a (big) desktop with 5 slots and a rack-mounted server with 11 slots. It had a sustained bandwidth of 108 MB/sec, 32-bit memory addressing and a 64-bit data-bus with ECC.

16 MB K-bus memory board

128 MB K-bus memory board

Monochrome circuitry

K-bus IO board

CG30 Semi-intelligent frame buffer

CG+ SGA40 Intelligent graphics system

S4000

S3000